#### **Comparators**

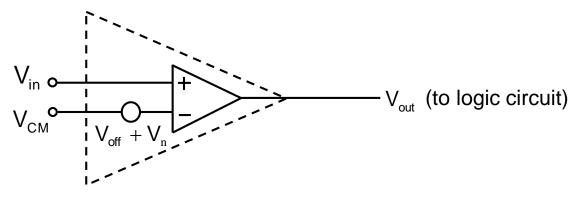

# Use An OPAMP as A Comparator

• Use for signal levels comparison to generate an output with a digital level

- Disadvantage

- Slow response: Settle too slowly for large voltage output

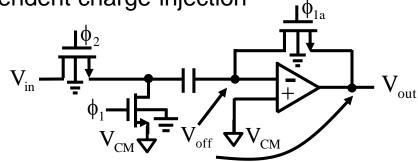

- Limited resolution: Due to input offset voltage

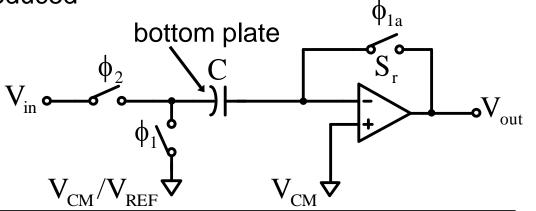

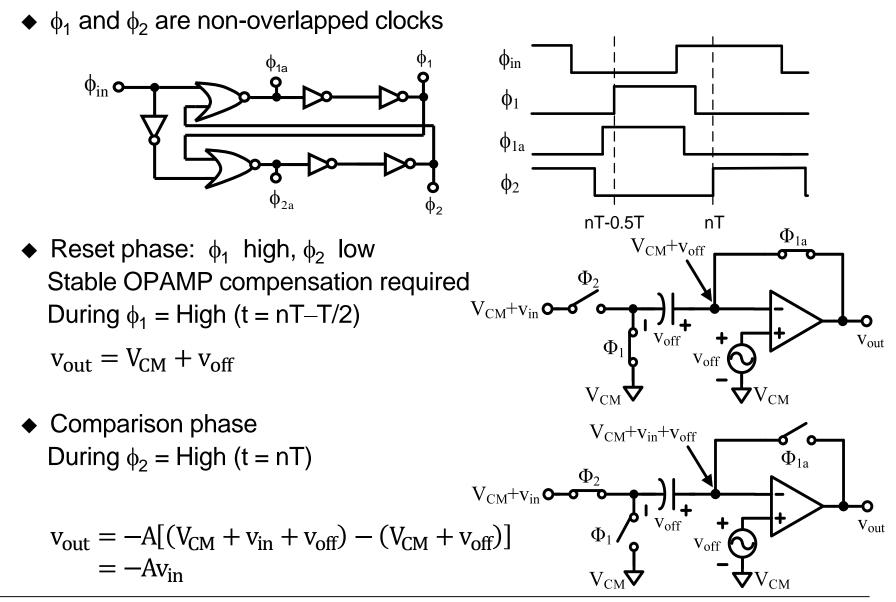

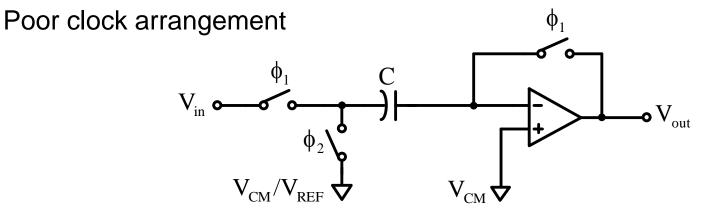

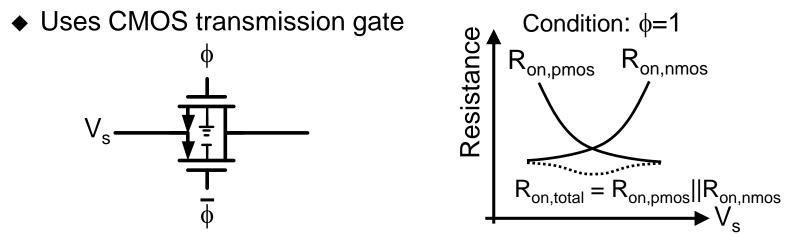

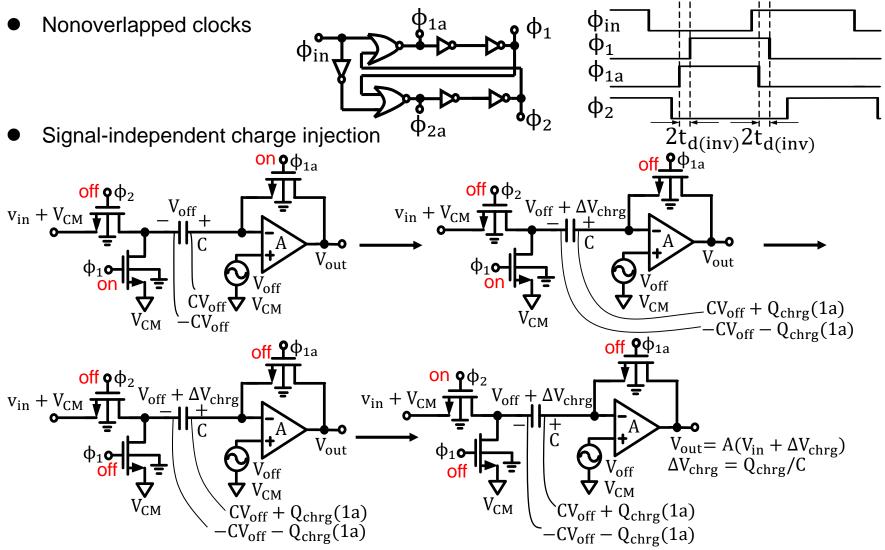

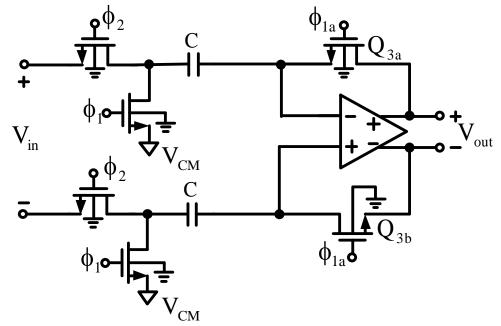

- Offset cancellation:  $\phi_{1a}$  is a slightly advanced version of  $\phi_1$  so that charge-injection effects are reduced

# Use An OPAMP as A Comparator (Cont.)

Prof. Tai-Haur Kuo, EE, NCKU, Tainan City, Taiwan

# Use An OPAMP as A Comparator (Cont.)

♦ If OPAMP noise is considered, then v<sub>off</sub> should be replaced by v<sub>off</sub> + v<sub>n</sub> (ignore the V<sub>CM</sub> noise)

V(nT) i.e. V(n)

> v<sub>out</sub>(nT) = -A[v<sub>in</sub>(nT)+v<sub>n</sub>(nT-T/2) -v<sub>n</sub>(nT)]

V(nT-T/2) i.e. V(n-T/2)

$$> v_{out}(nT) = -A[v_{in}(nT)+v_n(nT-T/2) - v_n(nT)]$$

V(nT-1/2) i.e. V(n-1/2)

V(nT-T) i.e. V(n-1/2)

>  $v_{out}(z) = -A[v_{in}(z)-v_n(z)(1-z^{-0.5})]$  (Correlated Double Sampling, CDS)

## Use An OPAMP as A Comparator (Cont.)

• No need for V<sub>in</sub> to charge C in the example above

•  $V_{in}$  needs to charge C during  $\phi_1$  is high

# **Correlated Double Sampling (CDS)**

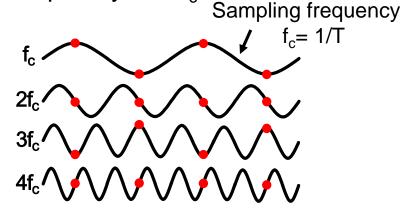

- Offset cancellation technique not only eliminates input offset voltage but also minimizes errors caused by 1/f noise

- Recall that

$$\begin{split} V_{\text{out}}(z) &= -A[V_{\text{in}}(z) - V_{\text{n}}(z)(1 - z^{-0.5})] \\ \text{Let } H_{\text{CDS}}(z) &= 1 - z^{-0.5} \\ \xrightarrow{z=e^{j\omega T}} H_{\text{CDS}}(z) &= 1 - e^{\frac{-j\omega T}{2}} = e^{\frac{-j\omega T}{4}} \cdot 2j\sin(\frac{\omega T}{4}) \ (e^{j\omega T} = \cos(\omega T) + j\sin(\omega T)) \\ \left| H_{\text{CDS}}(e^{j\omega T}) \right|^2 &= 4\sin^2(\frac{\omega T}{4}) \end{split}$$

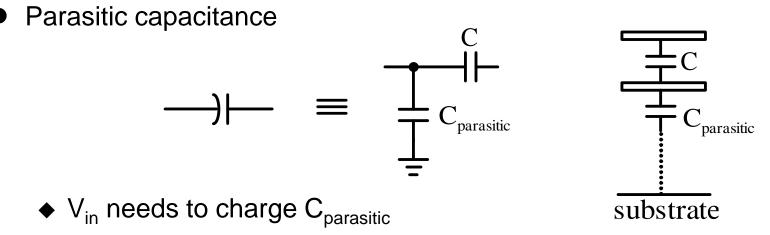

- From time domain waveform, if noise frequency =  $k \times f_c$

- When k is an odd number, noise cannot be canceled

- > When k is an even number, noise can be fully canceled

## **Correlated Double Sampling (CDS)**

Prof. Tai-Haur Kuo, EE, NCKU, Tainan City, Taiwan

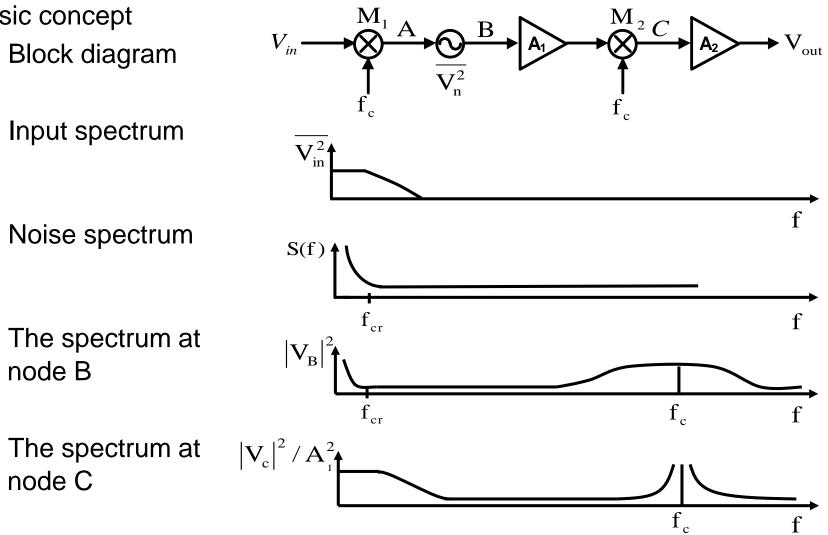

## **Chopper-Stabilized Amplifier**

- Can also be used to reduce 1/f noise

- **Basic concept**

- Block diagram

- Input spectrum

node B

node C

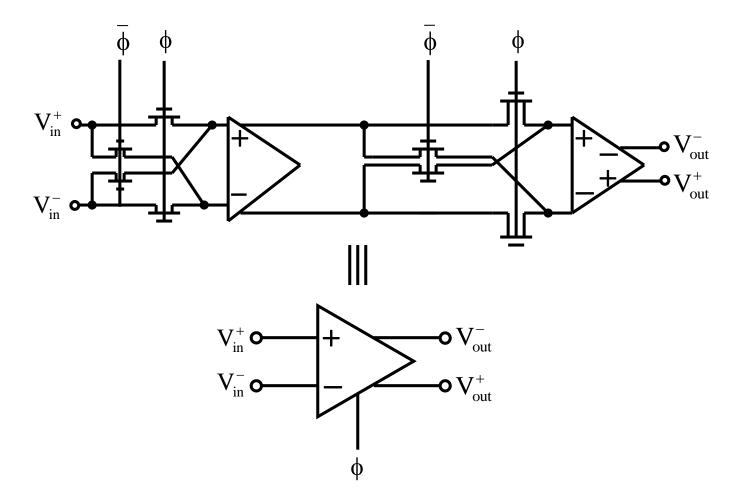

#### **Chopper-Stabilized Amplifier (Cont.)**

- Implementation example

- A differential chopper-stabilized OPAMP

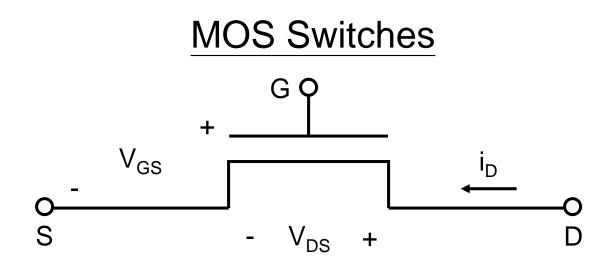

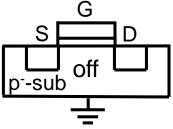

- Usual Case :  $|V_{GS} V_T| \gg |V_{DS}| \Rightarrow i = \mu C_{ox} \frac{W}{L} [(V_{GS} V_T)V_{DS} \frac{1}{2}V_{DS}^2]$

- MOSFET behaves like a linear resistor of value

$$R_{on} = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{GS} - V_T)}$$

- Gate control terminal

- Drain input/output

could be exchanged

• Source - input/output

#### **MOS Switches**

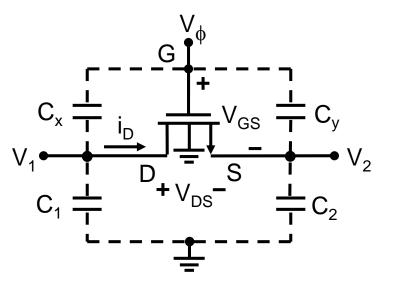

- Channel charge redistribution

- When switch is turned off, the channel charge is swept in part into drain and in part into source.

• Clock feedthrough

$$\Delta V_1 = \frac{C_x}{C_1 + C_x} \Delta V_{\varphi}$$

$$\Delta V_2 = \frac{C_y}{C_2 + C_y} \Delta V_{\varphi}$$

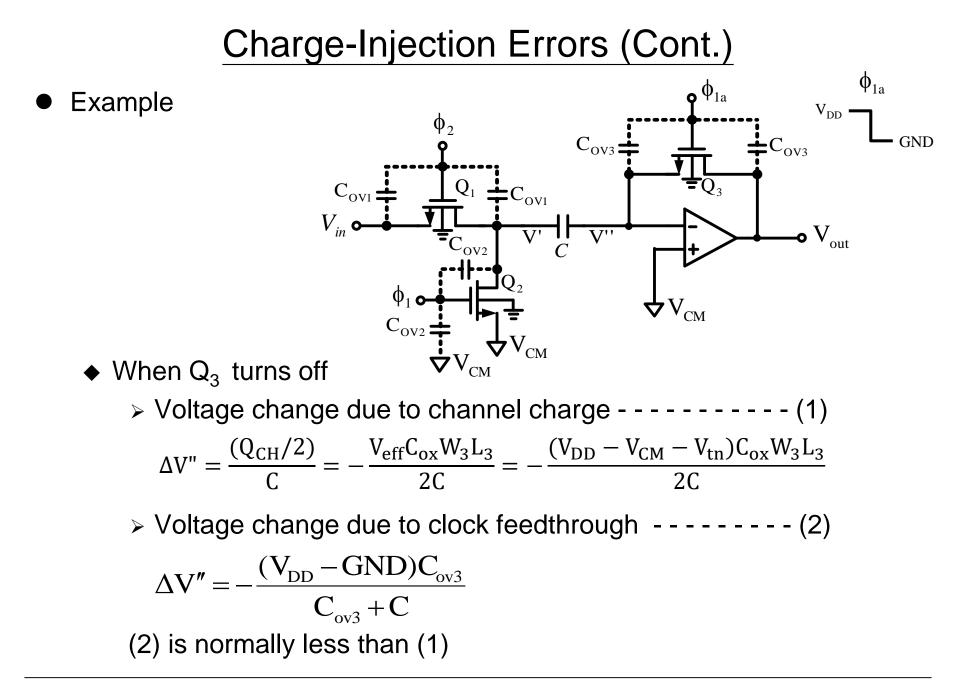

## **Charge-Injection Errors**

- Two major sources

- Channel charge of a transistor with  $V_{DS}=0$

$Q_{CH} = WLC_{ox}V_{eff} = WLC_{ox}(V_{GS} - V_{th}) = C_gV_{eff}$

- > MOS switches off  $\rightarrow$  Q<sub>CH</sub> flows from channel to drain & source junctions

- > For n-channel MOSFETs, channel charge is negative

- Clock feedthrough due to overlap capacitance C<sub>gs</sub> or C<sub>gd</sub>

(Channel charge injection dominates)

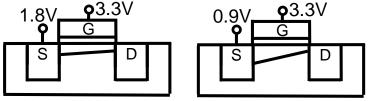

- Signal dependent charge-injection

- Example

Signal independent charge-injection

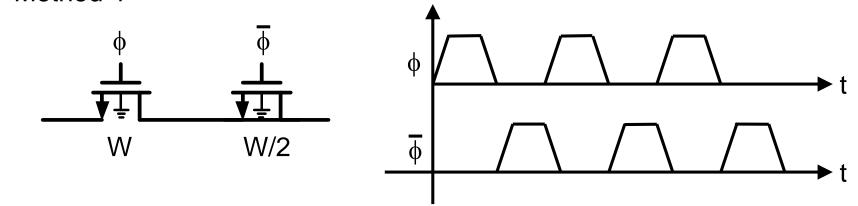

# Clock Feedthrough Charge-Injection Compensation

Method-1 :

• Method-2 :

• However, the distribution of the charge is unpredictable, this make perfect clock feedthrough compensation very difficult with any scheme.

#### Making Charge-Injection Signal Independent

Constant charge-injection error can be treated as a DC signal and thus can be ignored in most signal processing applications.

Prof. Tai-Haur Kuo, EE, NCKU, Tainan City, Taiwan

## Minimizing Errors Due to Charge-Injection

- Use larger C

- ♦ Large silicon area

- Large parasitic capacitance(Typically, ~20%C)

- Large power consumption

- Use fully differential design

- Errors will typically be at least ten times smaller than in the singleended case

# Minimizing Errors Due to Charge-Injection (Cont.)

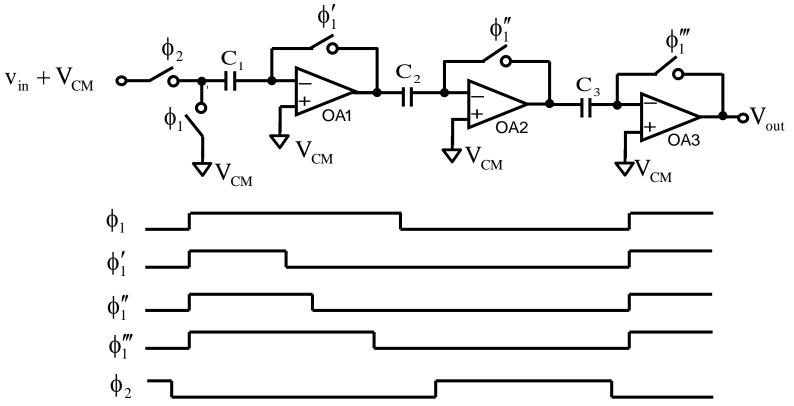

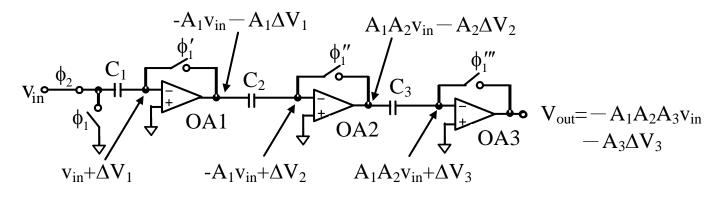

- Realize a multi-stage differential comparator (For simplicity, single-ended case is used for explanation)

- Very-high resolution comparator

- Multi-phase clocks, which slow down the circuit

# Minimizing Errors Due to Charge-Injection (Cont.)

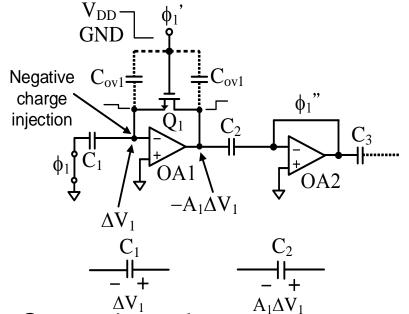

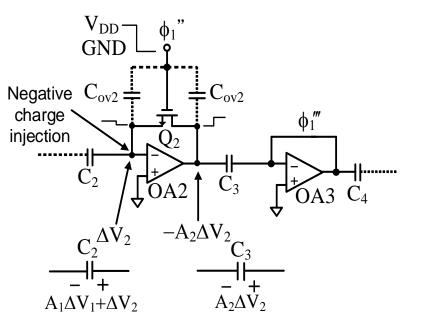

• When  $\phi_1$ ' turns off

• When  $\phi_1$ " turns off

Comparison phase

# Minimizing Errors Due to Charge-Injection (Cont.)

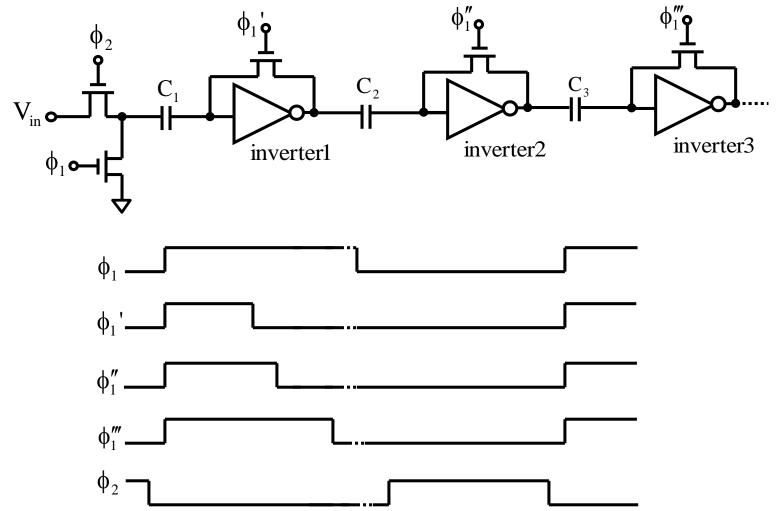

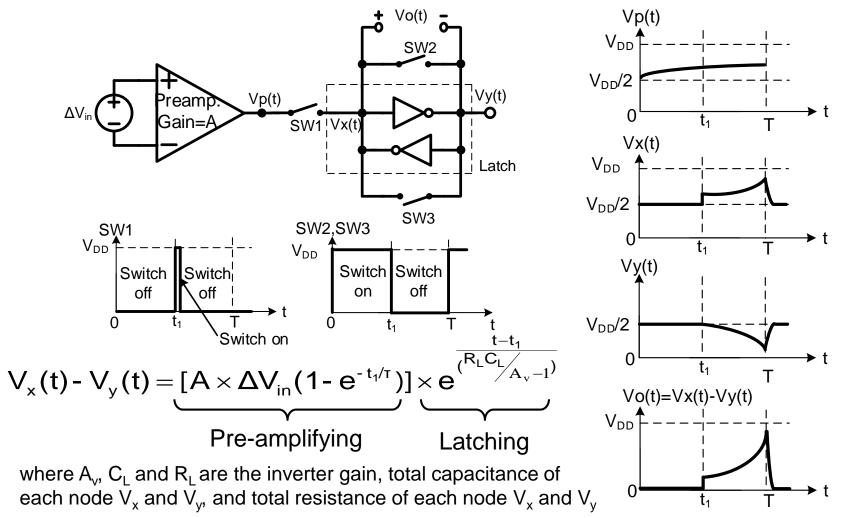

♦ A high-speed multi-stage comparator using inverters

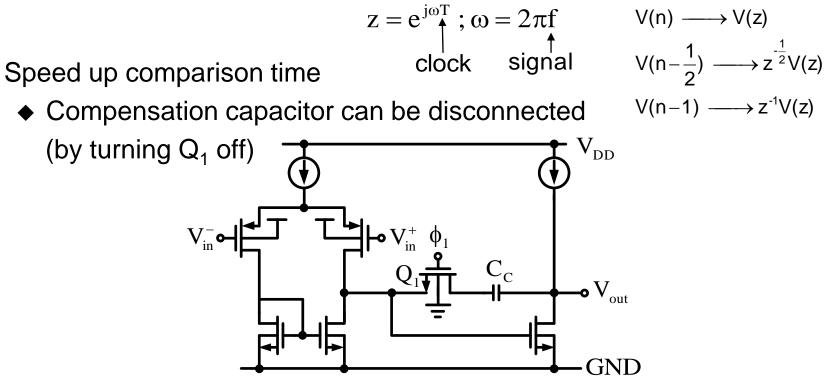

#### Speed of Multi-Stage Comparators

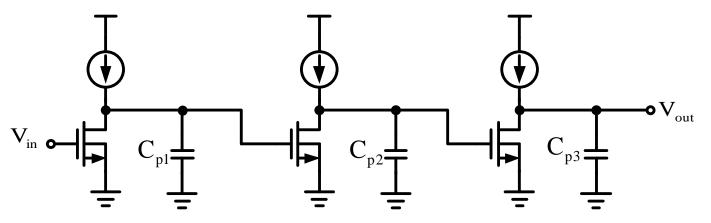

Typically, each stage consists of a single-stage amplifier that has only a 90<sup>o</sup> phase shift and therefore does not need compensation capacitors.

• The parasitic load capacitance at the output of the i<sup>th</sup> stage is approximately given by  $C_{pi} \cong C_{0-i} + C_{gs-i+1}$

where  $C_{0-i}$  is the output capacitance of the i<sup>th</sup> stage

$C_{gs\text{-}i\text{+}1}$  is the gate-source capacitance of the input transistor of the succeeding stage

• Normally  $C_{0-i} < C_{gs-i+1} \Rightarrow C_{pi} < 2C_{gs-i}$ Taking  $C_{pi}=2C_{gs-i}$  (as a worst case)

The transfer function of a single stage comparator (or amplifier) can be approximated as

$$A_i(s) = \frac{A_{0-i}}{1 + s/\omega_{p-i}}$$

where -3dB frequency

$$\omega_{p-i} \cong \frac{\omega_{t-i}}{A_{0-i}} \approx \frac{1}{A_{0-i}} \frac{g_{mi}}{2C_{gs-i}}$$

, where  $\omega_{t-i}$  is the unit gain frequency

Hence, time constant

$$\tau_{i} = \frac{1}{\omega_{p-i}} \approx \frac{2A_{0-i}C_{gs-i}}{g_{mi}}$$

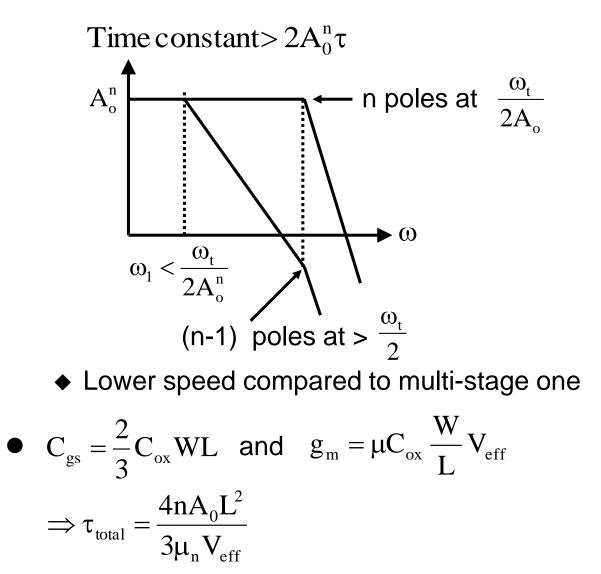

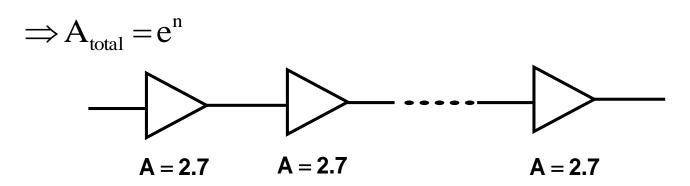

• The overall transfer function for a cascaded n-stage comparator

$$A_{\text{total}}(s) = \prod_{i} A_{i}(s) = \frac{A_{0-1} \cdot A_{0-2} \dots A_{0-n}}{\left(1 + \frac{s}{\omega_{p-1}}\right) \left(1 + \frac{s}{\omega_{p-2}}\right) \dots \left(1 + \frac{s}{\omega_{p-n}}\right)}$$

Ignoring higher-order terms results in

$$A_{\text{total}}(s) = \frac{\prod A_{0-i}}{1 + s(\sum_{i} \frac{1}{\omega_{p-i}})} \cong \frac{A_{0}^{n}}{1 + n\left(\frac{s}{\omega_{p-i}}\right)}$$

Time constant

$$\begin{split} \tau_{total} &\cong \frac{2nA_oC_{gs}}{g_m} \cong 2nA_o\tau_T = n\tau_i \\ \text{where} \quad & \tau_T = \frac{1}{\omega_T} = \frac{C_{gs}}{g_m}, \tau_i = 2A_0\tau_T \\ & \omega_T \text{ is unity-gain frequency of a single amplifier} \end{split}$$

• A single OPAMP with the same gain as the multi-stage comparator

Prof. Tai-Haur Kuo, EE, NCKU, Tainan City, Taiwan

$$\tau_{\text{total}} \cong 2nA_0\tau_t = 2n \cdot \sqrt[n]{A_{\text{total}}}\tau_t$$

Note:

$$\frac{\partial A^n}{\partial n} = A^n \ln(A)$$

For minimum  $\tau_{total}$

$$\frac{\partial \tau_{\text{total}}}{\partial n} = 2A_{\text{total}}^{1/n} \tau_t + 2n(-\frac{1}{n^2})A_{\text{total}}^{1/n} \tau_t \ln(A_{\text{total}}) = 0$$

$$\Rightarrow 1 - \frac{1}{n} \cdot \ln(A_{\text{total}}) = 0$$

$$\Rightarrow$$

n = ln(A<sub>total</sub>)

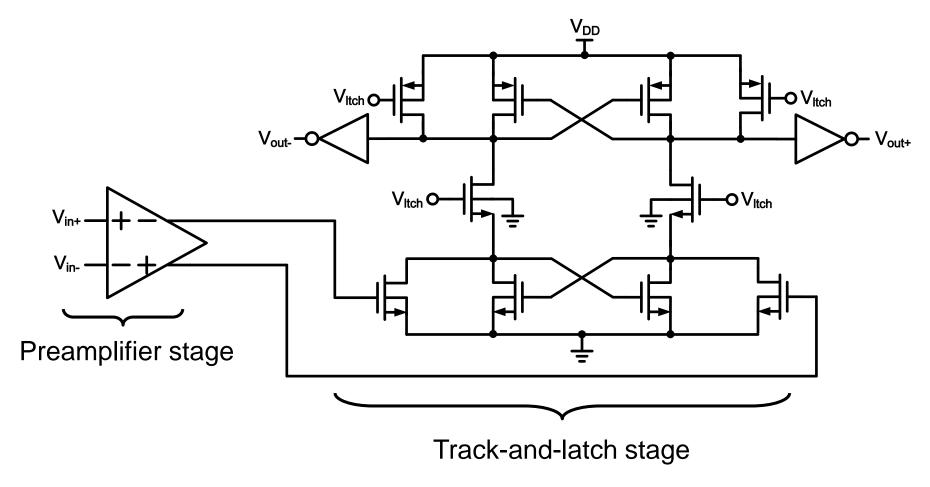

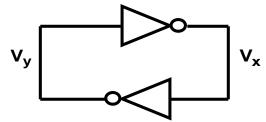

#### Latched Comparators

- Typical design: Preamplifier + track-and-latch stage

- ♦ A CMOS example

- Preamplifier

- 1 or 2 stages

- ♦ Two purposes

- > To obtain higher resolution

- > To minimize kickback effects

(kickback denotes the charge transfer either into or out of the inputs when the track-and-hold stage goes from track mode to latch mode)

• Typical gain : 4~10 gain

$$\uparrow \Rightarrow \begin{cases} resolution \uparrow \\ speed \downarrow \end{cases}$$

Without a preamplifier or buffer, the kickback will enter the driving circuitry and cause very large glitches, especially in the case when the impedance seen looking into the two inputs are not perfectly matched.

- Track-and-latch

- Amplifies preamplifier output

- Use positive feedback to generate full-scale digital signal (i.e. Its equivalent gain is infinite during latch phase)

- > Minimizes the total number of gain stages required

- Faster than the multi-stage approach

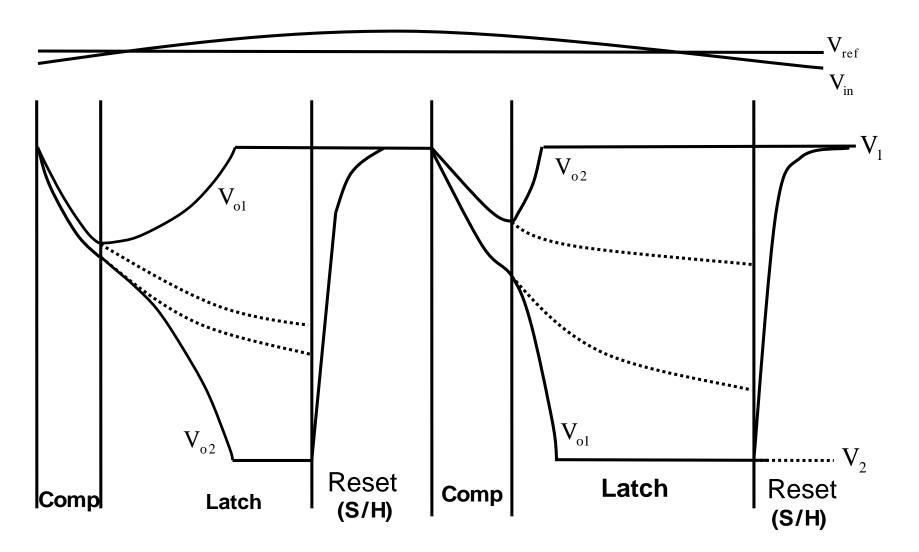

#### Comparator output waveform

- Capacitive coupling and reset switches can be included to eliminate any input-offset-voltage and clock-feedthrough errors, as described before.

- Hysteresis due to

- Circuit condition is not memoryless

eg. If a comparator toggles in one direction, it might have a tendency to stay in that direction.

- In order to eliminate it, one can reset the different stages before entering track mode.

- Input-transistor charge trapping

- (will be described later)

#### Latch-Mode Time Constant

• Simplified model of a track-and-latch stage in its latch phase

• Linearized model (low-frequency gain of inverter  $A_v = G_m R_L \Rightarrow G_m = \frac{A_v}{R_L}$ )  $\frac{A_v}{R_v} V_y \bigoplus C_L \bigoplus R_L \gtrless + V_x \qquad V_y + \end{Bmatrix} R_L \bigoplus R_L \bigoplus C_L \bigoplus \frac{A_v}{R_L}$

$$\frac{A_{v}}{R_{L}}V_{y} \bigoplus C_{L} \prod R_{L} + V_{x} \qquad V_{y} + R_{L} \prod C_{L} \bigoplus \frac{A_{v}}{R_{L}}V_{x}$$

$$\frac{A_{v}}{R_{L}}V_{y}(t) = -C_{L}\left[\frac{dV_{x}(t)}{dt}\right] - \left[\frac{V_{x}(t)}{R_{L}}\right]$$

$$\frac{A_{v}}{R_{L}}V_{x}(t) = -C_{L}\left[\frac{dV_{y}(t)}{dt}\right] - \left[\frac{V_{y}(t)}{R_{L}}\right]$$

#### Latch-Mode Time Constant (Cont.)

Let

$$\tau = R_L C_L$$

$\tau [\frac{dV_x(t)}{dt}] + V_x(t) = -A_v V_y(t)$  (1)

$\tau [\frac{dV_y(t)}{dt}] + V_y(t) = -A_v V_x(t)$  (2)

(2)  $-(1) \Rightarrow (\frac{\tau}{A_v - 1})[\frac{dV_o(t)}{dt}] = V_o(t)$

where  $V_o(t) = V_x(t) - V_y(t)$  is the voltage difference between the output voltages of the inverters

$$\Rightarrow V_{o}(t) = V_{o}(0)e^{(A_{v}-1)t/\tau}$$

where  $V_{\rm o}(0)$  is the initial voltage difference at the beginning of the latch phase

$$\Rightarrow \tau_{\text{latch}} = \frac{\tau}{A_{\text{V}} - 1} \cong \frac{R_{\text{L}}C_{\text{L}}}{A_{\text{V}}} = \frac{C_{\text{L}}}{G_{\text{m}}}$$

# $\begin{aligned} & \begin{array}{l} \mbox{Latch-Mode Time Constant (Cont.)} \\ & \left\{ \begin{array}{l} C_L = K_1 W L C_{ox} & ; & K_1 = 1 \sim 2 \\ G_m = K_2 g_m = K_2 \mu_n C_{ox} \frac{W}{L} V_{eff} & ; & K_2 = 1.5 \sim 2 \\ \end{array} \right. \\ & \Rightarrow \tau_{latch} = \frac{K_1}{K_2} \frac{L^2}{\mu_n V_{eff}} \end{aligned}$

$\Rightarrow \tau_{\rm latch}~$  depends primarily on the technology

For a voltage difference of ΔV<sub>logic</sub> to be obtained in order for succeeding logic circuitry to safely recognize the correct output value

$$T_{\text{latch}} = \frac{C_{\text{L}}}{G_{\text{m}}} \ln(\frac{\Delta V_{\text{logic}}}{V_{\text{o}}(0)}) = K_3 \frac{L^2}{\mu_{\text{n}} V_{\text{eff}}} \ln(\frac{\Delta V_{\text{logic}}}{V_{\text{o}}(0)})$$

If ∆V<sub>o</sub>(0) is small, this latch time can be large, perhaps larger than the allowed time for the latch phase. Such an occurrence is often referred to as metastability.

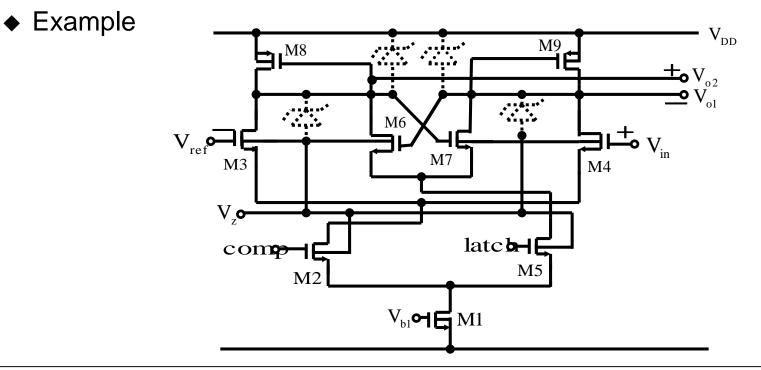

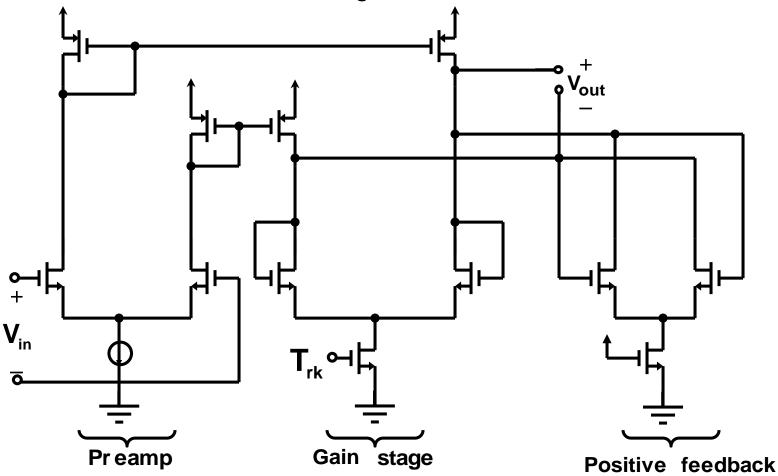

# Example of CMOS and BiCMOS Comparators

- Example-1:

- ♦ A comparator that has a preamplifier and a positive-feedback latch

Prof. Tai-Haur Kuo, EE, NCKU, Tainan City, Taiwan

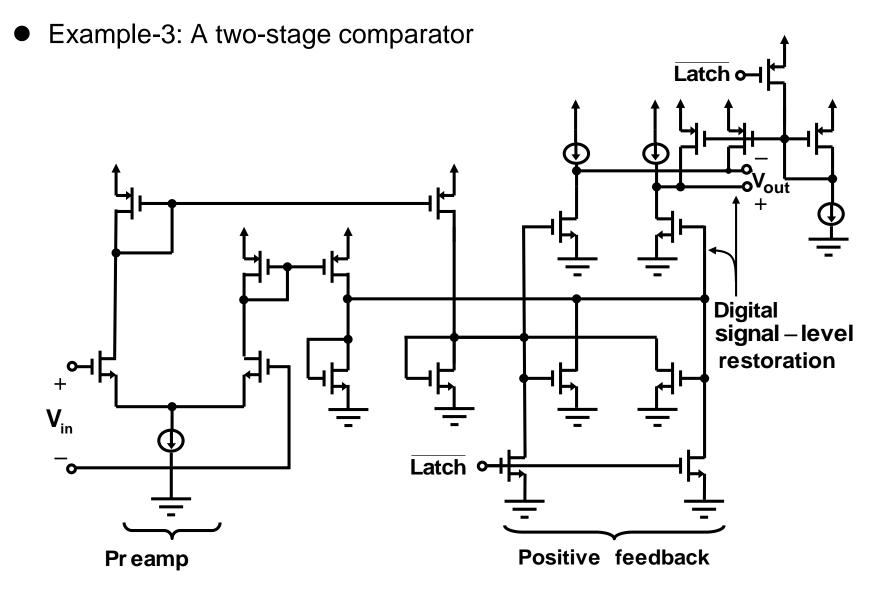

# Examples of CMOS and BiCMOS Comparators (Cont.)

- Example-2:

- A two-stage comparator that has a preamplifier and a positivefeedback track-and-latch stage

Prof. Tai-Haur Kuo, EE, NCKU, Tainan City, Taiwan

# Examples of CMOS and BiCMOS Comparators (Cont.)

# Input Transistor Charge Trapping

- When n-channel transistors are stressed with large positive gate voltages, electrons can become trapped via a tunneling mechanism in which electrons tunnel to oxide traps. During the time they are trapped, the effective transistor threshold voltage is increased. This leads to a comparator hysteresis on the order of 0.1 to 1mV.

- The time constant for the release of these trapped electrons is on the order of milliseconds and is much longer than the time it takes for them to become trapped.

- This effect correlates well with transistor 1/f noise and is much smaller in p-channel transistors.

- P-channel transistor exhibit much less hysteresis than n-channel transistors.

# Input Transistor Charge Trapping (Cont.)

- One approach of minimizing this effect is to flush the input transistors after each use where the junctions and wells of n-channel transistors are connected to a positive power supply whereas the gates are connected to a negative power supply. This effectively eliminates the trapped electrons.

- Alternately, two input stages can be used for the comparator— a rough stage can be used during times when large signals with overloads are possible, whereas a fine stage can be used during times when accurate comparisons are necessary and it can be guaranteed that no large signals are present.